IBM Research

3Dチップ製造のサプライチェーンを簡素化する画期的な技術を発表

2022年7月20日

カテゴリー IBM Research

記事をシェアする:

IBM Researchと東京エレクトロンは、3Dチップ積層技術によってウェハー生産のサプライチェーンおよびプロセスを簡素化するチップ製造イノベーションを目指し、パートナーシップを締結しました。

コンピューター・チップの需要はかつてないほど高まっていますが、この2年間で、世界的なサプライチェーンは前例のない重圧を受けています。しかし、実際には、それ以前からコンピューター・チップ業界には重圧がありました。 ムーアの法則は、マイクロチップ上のトランジスターの数が毎年2倍になると予測していますが、シリコンの物理的限界に近づくにつれ、チップ製造者がその予測通りに集積度を高め続けることは困難になりつつありました。 例えば、IBM Researchの最新のチップ・ノードは、2ナノメートルです。

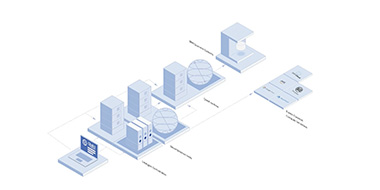

私たちの最新のブレークスルーは、チップ製造のサプライチェーンを簡素化するために、どのようにチップを積層することができるかに関わるものです。本日、当社は、東京エレクトロン株式会社(以下、東京エレクトロン)と共同で、世界で初めて300mmシリコン・ウェハーの新しい3次元積層技術の導入に成功したことを発表します。チップ積層は、現在、広帯域メモリの製造などハイエンドな分野での採用にとどまっていますが、従来のムーアの法則で考えられてきた単位面積当たりではなく、単位体積当たりのトランジスタ数を増大する可能性を持っています。

3Dボリュームの進化

チップ積層構造では、Si貫通電極(TSV)と呼ばれるシリコン・チップ間の垂直接続を必要とします。これらの微小接続により、1つのシリコン・チップから別のシリコン・チップへ電流を流すことが可能になり、各層のチップが他の層のチップと通信できるようになります。垂直積層を実現するプロセスでは、TSVの電極を露出してTSVを完成させるためにシリコン・ウェハー裏面を薄化することが必要となります。チップ積層を構成する各層は非常に薄く、通常は厚さ100ミクロン未満です。

このように壊れやすく柔軟なシリコン・ウェハーを生産プロセスで扱うために、各ウェハーはキャリア・ウェハーと呼ばれるものに接合されます。 現在のチップ製造では、通常これらのキャリア・ウェハーはガラス製で、シリコン・ウェハーを一時的に接合し、ウェハーが破損することなく処理できるようになっています。 ウェハーの加工が終わると、ガラス・キャリアは紫外線レーザーを用いてシリコン・ウェハーから剥離されます。場合によっては、シリコン・キャリア・ウェハーを使用することがありますが、これには、分離を容易にするための機械的な剥離プロセスを使用する必要があります。これにより、破損が発生し、歩留まりを低下させる可能性があります。

IBMと東京エレクトロンは共同で、シリコンに対して透過的な赤外線レーザーを使用して新しい300 mmウェハーの剥離プロセスを構築しました。つまり、ガラス・ウェハーの代わりに標準的なシリコン・ウェハーをキャリアに使用できるようになります。

私たちの新技術により、シリコン・ウェハーを他のシリコンに接合することができ、ガラス・キャリアを生産ラインに導入する必要がなくなりました。 また、貼り合わされたシリコン・ウェハーのペアに関連した加工の利点もあります。例えば、製造装置の互換性やウェハー・チャッキングの問題をなくし、加工中の欠陥を減らし、素材の異なるウェハーのペアに関連するプロセスの問題を減らし、薄化されたウェハーのインライン・テストを可能にするといった利点です。 このテクノロジーにより、シリコン間の相互接続を用いた先進的なFOWL(Fan-out wafer level)技術や3Dチップレット技術を実現し、将来的にもこれらの技術を大きく発展させることができるようになります。

IBM Researchは、この新しいタイプのレーザー剥離を完全なものにするために、2018年から東京エレクトロンと連携しています。これは、20年以上に渡るパートナーシップにおける最新のコラボレーションに過ぎません。新しいシリコン・チップを大規模に製造するために必要な製造装置を設計するエキスパートである東京エレクトロンは、2018年以降、このプロセス・テクノロジーを採用し、300mmウェハーのシリコン・ウェハー・ペアを剥離および分離することができる新規の大量生産用製造装置の設計および製作を行いました。

私たちは共同で、ニューヨーク州オールバニに製造装置システムの試作機を設置しました。オールバニには、私たちが主導的な役割を担う半導体の生産、設計、および製造に関する優れた研究開発のエコシステムがあります。 この環境において、試作機のさらなる検証を実施して、このプロセスが全体の半導体製造フローにどのように実装されるかを実証し、さらに、このプロセスを使用して構築された3Dチップ積層そのものの実証を行います。

世界的にチップ不足が続く中で、今後数年にわたり、チップの生産能力を高めるための斬新な方法が必要となっています。 私たちは、半導体サプライチェーンに必要な製品の数を削減するとともに、今後何年もの間、処理能力の向上を促進できるものと期待しています。

東京エレクトロンについて

東京エレクトロンは、革新的な半導体製造設備のグローバル企業として、幅広い製品分野で開発、製造、販売を行っています。 東京エレクトロンの半導体製造設備の生産ラインはすべて、それぞれの対応するグローバル・セグメントにおいて高い市場シェアを維持しています。 東京エレクトロンは、米国、ヨーロッパ、およびアジアのグローバル・ネットワークを通じて、お客様に優れた製品とサービスを 提供しています。東京エレクトロンについて詳しくは、https://www.tel.co.jp/ を参照してください。

本記事は「The breakthrough that could simplify the 3D chipmaking supply chain」を抄訳し、日本向けに加筆したものです。

東京基礎研究所 ニューロモーフィック・インターコネクション担当マネージャー。IBM Academy of Technologyメンバー。

入社以来、先端半導体パッケージの開発に従事し、CPU、カスタムロジック半導体等のパッケージの製品化を手掛ける。現在は、AIアクセラレータ半導体向けの高密度異種チップ集積(ヘテロジニアス・インテグレーション)技術の研究に注力する。

女性技術者がしなやかに活躍できる社会を目指して 〜IBMフェロー浅川智恵子さんインタビュー

ジェンダー・インクルージョン施策と日本の現状 2022年(令和4年)4⽉から改正⼥性活躍推進法が全⾯施⾏され、一般事業主⾏動計画の策定や情報公表の義務が、常時雇用する労働者数が301人以上の事業主から101人以上の事業主 […]

Qiskit Runtimeで動的回路を最大限に活用する

私たちは、有用な量子コンピューティングのための重要なマイルストーンを達成しました: IBM Quantum System One上で動的回路を実行できるようになったのです。 動的回路は、近い将来、量子優位性を実現するため […]

Qiskit Runtimeの新機能を解説 — お客様は実際にどのように使用しているか

量子コンピューターが価値を提供するとはどういうことでしょうか? 私たちは、価値を3つの要素から成る方程式であると考えます。つまりシステムは、「パフォーマンス」、「機能」を備えていること、「摩擦が無く」ビジネス・ワークフロ […]