量子コンピューティング

ISA回路とは

2024-05-01

カテゴリー IBM Research (コンピューティング) | 量子コンピューティング

記事をシェアする:

Qiskit Runtimeプリミティブの最近の更新について

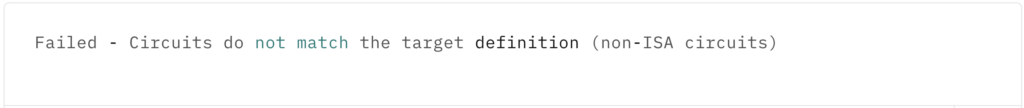

Qiskit Runtime プリミティブの最近の更新により、プロジェクトでバックエンドに回路を投入した時に、目新しいエラーメッセージに遭遇することがあります。

このエラーメッセージでは、問題を緩和するためのいくつかの提案を列挙していますが、何が起こっているのかを詳しく説明してはいません。実際のところ、ここでは何が起こっているのでしょうか。

Qiskit Runtimeの最新バージョンでは、新しい要件が導入されました。バックエンドに投入されるすべての回路は、バックエンドの Target の制約に準拠しなければならないというものです。すなわち、投入された回路は、バックエンドの Instruction Set Architecture(ISA)、すなわちデバイスが理解し実行できる命令セット、に基づいて記述されていると想定されます。これらの Target の制約は、デバイスにネイティブの基本ゲート、量子ビット間の接続関係、および、場合によっては、パルスやその他の命令タイミングの仕様といった要素によって定義されています。

このブログ・ポストでは、この新しいISA回路エラーメッセージに遭遇しているQiskitユーザーの方に対して、クイックで簡単な解決策を提供し、原因となっている変更の理由を説明します。

問題解決のための作業

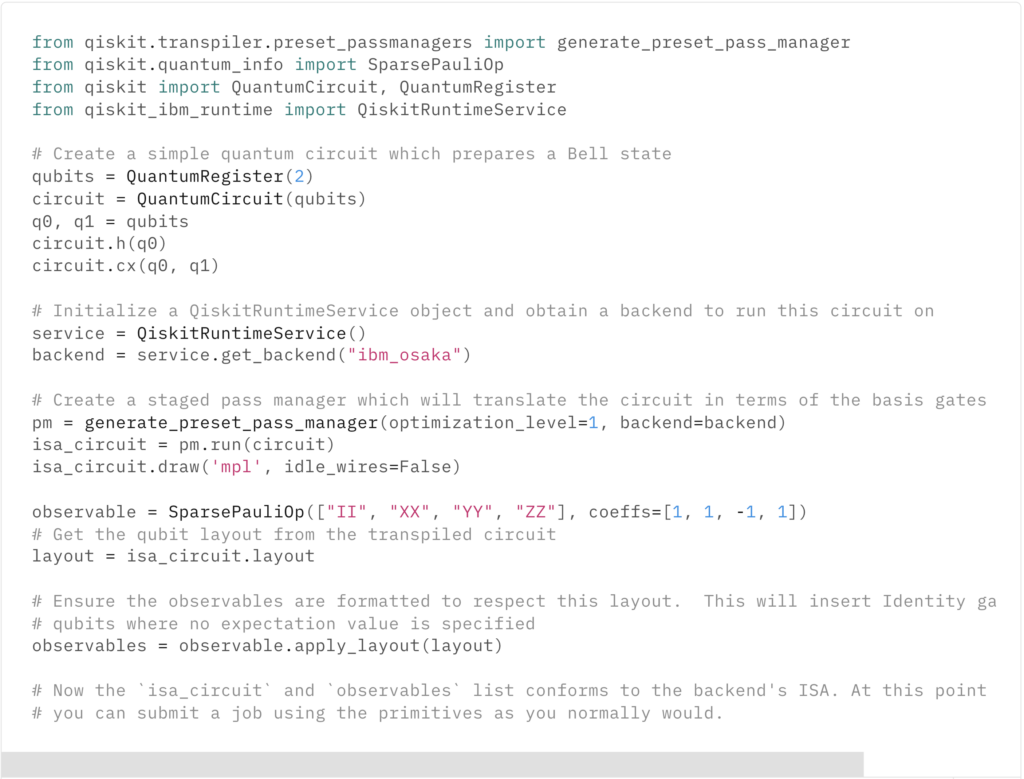

ひとことで要約すると、上のようなエラーに遭遇した場合、自分で作成した pass managerか、プリセットのpassmanagerのいずれかを使用して回路をトランスパイルする必要があります。pass managerが出力した回路はデバイスの制約に準拠するようになり、Sampler プリミティブを使用している場合にはそれだけで問題が解消するはずです。Estimator を使用している場合は、あなたが与えたオブザーバブルを、選択した量子ビットのレイアウトに合わせるために追加のステップを踏む必要があります。それはたとえば、SparsePauliOp オブジェクトとして保存されているオブザーバブルの場合は apply_layout メソッドを使用することで行います。でも、これでおしまいです。

このエラーメッセージを消す方法を知りたいというただそれだけでこの記事に来たのであれば、必要なことは以上です。以下のコードは、バックエンドの制約に準拠した回路とオブザーバブルを準備する簡単な例を示しています。

好奇心旺盛な読者の皆様には、このブログの残りで、これらのターゲット・バックエンドの制約がどこから来ているのか、ISA回路要件が導入された理由をより深く掘り下げてご説明します。

Targetとは?

Targetオブジェクトは、qiskit.transpilerサブモジュール内で主に使用されます。このオブジェクトには、特定のバックエンドの制約に関してトランスパイラー・パスが必要とする重要な情報がすべて含まれています。それはたとえば、そのハードウェアにおける各量子ビットの基本ゲートや、利用可能な2量子ビット・ゲートのネイティブな方向などです。

たいていの場合、実験を実行する時に Targetオブジェクトについて気にする必要はありません。なぜなら、Qiskit IBM RuntimeのQiskitRuntimeServiceを使用すれば、それらの情報はBackendV2の属性として含まれているからです。IBM Quantum™ Platform上のすべてのバックエンドには、デフォルトでそれぞれのTargetが定義されています。

このことからひとつの疑問が生じるかもしれません。すなわち、バックエンドのTarget属性がデバイスの利用可能な命令に関するすべての関連情報を含んでいるのなら、デバイスのBackendV2オブジェクトにはどのような情報が含まれているのか、ということです。

答えは、BackendV2は、プリミティブ・クエリーの投入や過去のジョブの実行結果の照会といった、サービスやシミュレーターとのやりとりを行うためのフックを提供しているということです。また、デバイスの動作をモデル化するための特性データをユーザーが要求することも可能にしています。つまり、BackendV2はTargetをサービスに結びつけているのです。

なぜこのような変更が行われたのか

ISA回路要件が導入されたのは、私たちのマシンの全体的な効率を高めるための継続的な取り組みの一環としてです。IBM Quantumのユーザー数は過去数年間に大きく増加しました(これは素晴らしいニュースです)。そのこともあって、私たちは量子コンピューターがユーザーにとって、可能な限りいつでも利用可能であるようにしたいのです。

回路がバックエンドの制約に準拠しなければいけないという要件を導入することで、ある種のフィルター・システムのようなものが実現されます。この新しい要件は、デバイスが実行できないような回路を含むジョブが、デバイスに投入されないように効率的にフィルタリングします。これは結局のところデバイスの可用性を高め、キュー時間を短縮します。また、新しいISA回路要件のもう一つの利点は、回路実行の予測可能性を改善するということです。ジョブを投入する前にユーザーが回路をトランスパイルすれば、回路実行時の不明確で時間がかかるかもしれないステップを削除することになります。

新しい要件には、クエリーのコストについてのユーザーの理解を深める効果もあります。投入されるクエリーのコストを簡単に理解できることは重要です。抽象的なオラクルを使う回路(すなわち、ターゲット・デバイスを考慮していない、抽象度の高い命令セットで書かれた回路)を投入すると、その回路がISA形式ではコンパクトに表現されるのか、あるいは指数関数的に大きいのかに気づくことができません。まずトランスパイルすることで、回路の深さやエンタングル・ゲート数など、そのISA回路のプロパティーを調べることができます。これによって、プリミティブ・クエリーに関して想定しないような結果になることが少なくなります。

この記事が、新しいISA回路要件が導入された理由や、Qiskit SDKとIBM Qiskit Runtimeで重要な役割を持つISA回路についての疑問の解消にお役に立つことを願います。ISA回路についてのさらなる詳細については、トランスパイレーションについてのドキュメントやV2プリミティブのマイグレーション・ガイドもチェックしてみてください。

この記事は英語版IBM Researchブログ「What are ISA circuits?」(2024年4月17日公開)を翻訳し一部更新したものです。

量子中心のスーパーコンピューターに必要なサーキット・カッティングを可能にするダイナミック・サーキット

Natureに掲載された新しい論文は、一つの量子プロセッサーでは実行不可能なサイズの量子回路を、二つの量子プロセッサーを接続して実行できることを世界で初めて示しました。 今日、世界で最も強力な古典的スーパーコンピューター […]

2年前に設定したチャレンジを達成した IBM Quantum

今回が初回となる IBM Quantum Developer Conferenceで、IBMはアルゴリズム探索を容易にする高性能な量子コンピューターと使いやすい量子ソフトウェアを発表しました。 IBM®は 2年前に、量子 […]

量子中心のスーパーコンピューティングの実現

(特別な工夫のない)愚直な古典計算では扱えないレベルの大規模な問題を解決できる能力を持った 実用規模の量子コンピューターが、ハイパフォーマンス・コンピューティングの未来を変えていきます。 歴史上初めて、コン […]