量子コンピューティング

実用規模のワークロードで量子回路の深さを削減するフラクショナル・ゲート

2024-11-18

カテゴリー IBM Research (コンピューティング) | 量子コンピューティング

記事をシェアする:

フラクショナル・ゲートは、実用規模の実験の効率を向上するのに役立つ新しいタイプの量子論理ゲートです。

IBM® は、IBM Quantum Heron™ QPUに新しい種類の量子論理ゲートを導入します。それらは「フラクショナル・ゲート」と呼ばれ、量子ワークロードの回路の深さを削減するための強力な新しい道具になります。フラクショナル・ゲートは、実用規模の量子実験を構築する新たな効率的手段をもたらします。これは自然現象をシミュレートするように設計された量子実験に特に効果的です。では、どのように機能するのでしょうか?

100量子ビット以上と数千のゲートを使用する大規模な実験を実行する場合、さまざまな手段をとって量子回路の深さを削減することが重要です。回路が短くなれば、今日のノイズがある量子ハードウェアを用いてより大きなシミュレーションを実行することができます。 フラクショナル・ゲートは、回路の深さを削減するのに有用な、2つの新しい ISA命令を IBMの量子コンピューターに追加します。

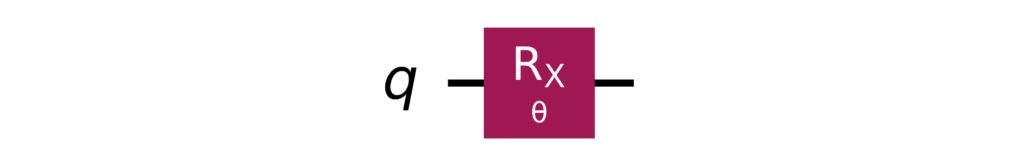

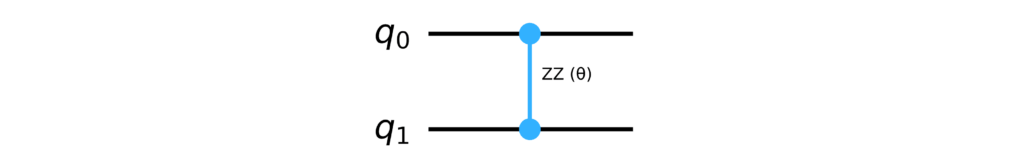

これらの新しい ISA命令により、RX(θ) ゲートまたは RZZ(θ) ゲートの形式で、1量子ビット回転 または 2量子ビット回転を実行できるようになります。これらのゲートを使用すれば、たとえば量子系のダイナミクスをシミュレートするのに使用する量子回路のように、1量子ビット回転または2量子ビット回転を含むあらゆる量子回路でゲート数を大幅に減らすことができます。

IBM Quantum QPU のパルス・レベル制御に関する重要なご案内

フラクショナル・ゲートの導入と並行して、全ての IBM Quantum QPUでパルス・レベル制御のサポートを廃止する予定であることをお知りおきください。

2025年 2月 3日に、パルス・レベル制御がサービスから削除されます。この決定は、実用規模の実験と量子優位性の探索をサポートするための、より高レベルのサービスに IBMの資源と労力を集中するための継続的な取り組みの一環です。

最適制御の研究のために IBM Quantumのパルス・レベル制御機能を使用している方には、Qiskit Dynamicsなどのツールやリソースの使用を検討することをお勧めします。Qiskit Dynamicsは、シミュレーションにおいてそのような研究を可能にすることで代替手段になる可能性があります。

この廃止機能についてこのブログで説明するのは、パルス・レベル制御の最も一般的なユース・ケースの一つが、この記事で説明している 1量子ビットあるいは 2量子ビットの回転を直接実装することだからです。 新しいフラクショナル・ゲートが、その機能を置き換える便利な代替手段であることが、以下の記事でお分かり頂けます。

従来の RX(θ) および RZZ(θ)ゲートはなぜ非効率なのでしょうか?

フラクショナル・ゲートが、最終的な回路の深さにもたらす計算コスト削減を理解するために、RX(θ) および RZZ(θ) ゲートを Qiskitトランスパイラが通常どのように分解するか見てみましょう。最初に、RX(θ) ゲートと RZZ(θ) ゲートをそれぞれ含んだ 2つの回路を作成します。 RX(θ) ゲートは次の通りです。

from qiskit.circuit import Parameter

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

rx_qc = QuantumCircuit(1)

param = Parameter(‘θ’)

rx_qc.rx(param, 0)

rx_qc.draw(‘mpl’)

次に、RZZ(θ) ゲートを示します。

rzz_qc.rzz(param, 0, 1)

rzz_qc.draw(‘mpl’)

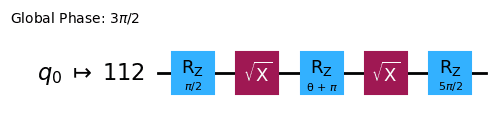

次に、それらをトランスパイルすると、RX(θ) ゲートは次のようになります。

# Decomposition of an RX(θ) gate using the IBM Quantum QPU basis

service = QiskitRuntimeService()

backend = service.backend(“ibm_torino”, use_fractional_gates=True)

pm = generate_preset_pass_manager(optimization_level = 3, backend=backend)

rx_transpiled_circuit = pm.run(rx_qc)

rx_transpiled_circuit.draw(‘mpl’, idle_wires=False)

ここのようにゲートの深さが かなり増加していることがご覧いただけます。たった 1つの量子論理ゲートが 5つになり、回路も 5倍のサイズになりました。

この場合、√X ゲートのみがゲート・エラーに寄与していることに注意する必要があります。これは、IBM Quantumのマシンで RZゲートを実行する独特の方法によるものです。さらに、√Xゲートのみを考慮した場合においても、元のゲートの深さの 2倍であり、100量子ビット以上を含む回路で考えると、この倍増が大問題になります。

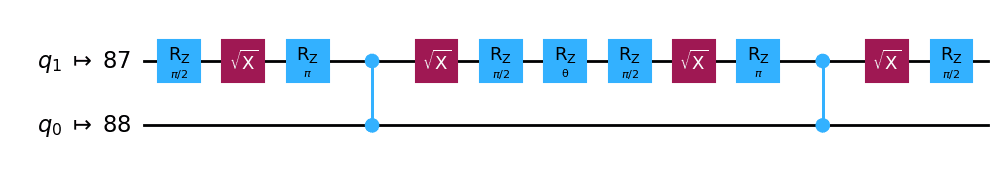

次に、RZZ(θ) ゲートがどう分解されるか見てみましょう。

rzz_transpiled_circuit.draw(‘mpl’, idle_wires=False)

これはさらに大きな増加です! RZZ(θ)ゲートを実行するには、CNOTゲートの動作を行う 2つの CZゲートと、いくつかの 1量子ビット・ゲートを実行する必要があります。

これに対し新しいフラクショナル・ゲートを使用すると、これらの 1量子ビットおよび 2量子ビットの回転を直接実行でき、回路の深さの増加というこの問題を避けることができます。

フラクショナル・ゲートの使用法: イジング・モデルに基づく簡単な例

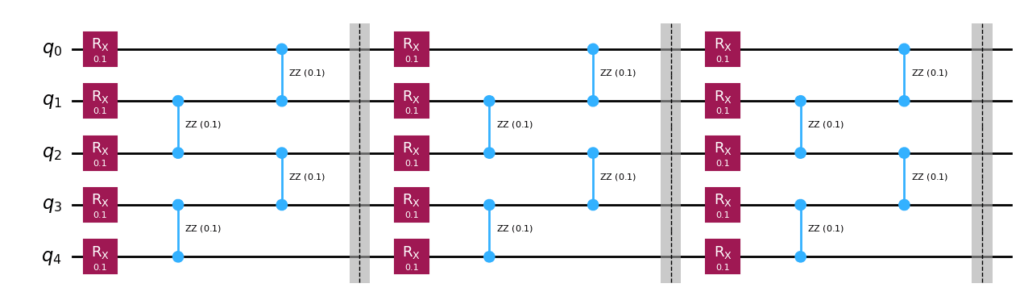

新しいフラクショナル・ゲート命令の使用方法を簡単に見てみるために、横磁場イジング模型(transverse field Ising model)のダイナミクスをシミュレートする回路を例として見てみましょう。これはシミュレートするのが比較的単純な量子系であり、フラクショナル・ゲートの威力を示すのに役立つ実用的なケーススタディになります。

このモデルでは、各量子ビットは、1次元の線あるいは2次元格子内の 1サイトに対応します。 この例ではモデルのサイトを1次元鎖で表現した量子系の時間発展をシミュレートしてみましょう。次のように回路を構築できます。

from qiskit import QuantumCircuit

num_qubits = 5

num_time_steps = 3

rx_angle = 0.1

rzz_angle = 0.1

ising_circuit = QuantumCircuit(num_qubits)

for i in range(num_time_steps):

# rx layer

for q in range(num_qubits):

for q in range(1, num_qubits-1, 2):

# 2nd rzz layer

for q in range(0, num_qubits-1, 2):

ising_circuit.barrier()

ising_circuit.draw(‘mpl’)

さて、フラクショナル・ゲートを有効活用するためにしなければいけないことは、サポートしているバックエンドを指定するだけです!そうするだけで、あとはトランスパイラが面倒を見てくれます。

from qiskit_ibm_runtime import QiskitRuntimeService

service = QiskitRuntimeService()

backend_fractional = service.backend(“ibm_torino”, use_fractional_gates=True)

pm_fractional = generate_preset_pass_manager(optimization_level=3, backend=backend_fractional)

ising_circuit_transpiled = pm_fractional.run(ising_circuit)

ising_circuit_transpiled.draw(‘mpl’, idle_wires=False)

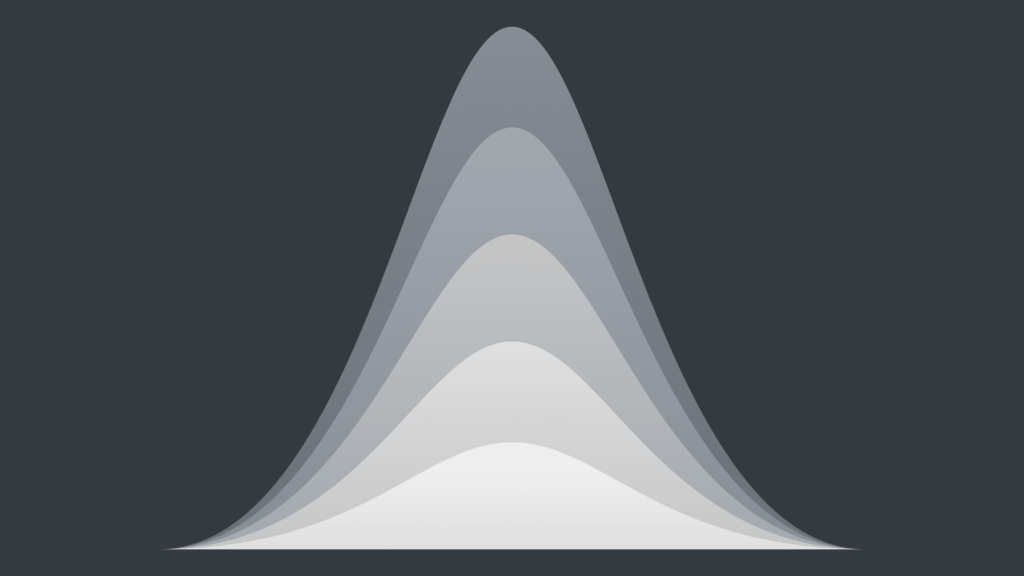

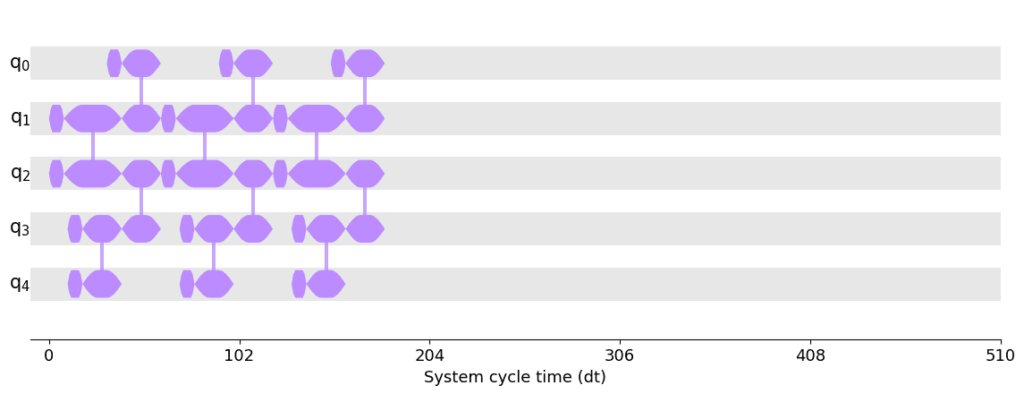

この違いを確認するために、フラクショナル・ゲートをサポートしているバックエンドと、サポートしていないバックエンドでスケジュールされた回路時間を比較します。フラクショナル・ゲートを使用すると、以下の結果になります。

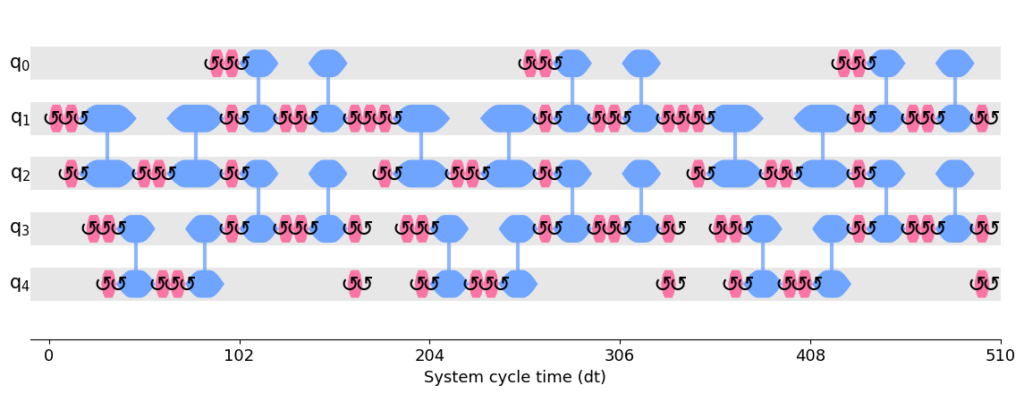

次に、フラクショナル・ゲートなしの場合はこちらです。システム・サイクル・タイムは2倍以上に増えています。

フラクショナル・ゲートの制限事項

フラクショナル・ゲートは強力なツールですが、留意すべきいくつかの制限があります。例えば、フラクショナル・ゲートはすべてのバックエンドで使えるわけではありません。以下のコードを使用して、どのバックエンドがサポートしているかを確認できます。

for backend in service.backends():

if ‘rzz’ in backend.target.operation_names:

あるいは、以下のようなコードを使ってフラクショナル・ゲートをサポートしているバックエンドを照会することもできます。

この 2番目のコード例は最初の例と同じことを行いますが、詳細を表示しません。同じ filtersを least_busy関数に渡すことができます。

もう 1 つの考慮事項は、少なくとも現時点では、動的回路(ダイナミック・サーキット)と組み合わせてフラクショナル・ゲートを使用できないことと、および PEC、ZNE with PEA、または PauliトワリングなどのQiskit Runtime Primitivesで使用可能なエラー緩和手法とフラクショナル・ゲートを併用できないことです。しかし、ダイナミック・デカップリングおよび T-REx手法と併せてフラクショナル・ゲートを使用することはできるようになる予定です。 将来には今のような制限を緩和できる可能性があります。

こちらにある資料で、フラクショナル・ゲートと併用できないエラー緩和手法と併用できる手法の概要を示す便利なチャートをご覧いただけます。

フラクショナル・ゲートを使い始めるには

新しいフラクショナル・ゲートで実験をしてみて、実用規模のワークロードのゲート深さを削減するのにどのように役立つかをぜひご確認ください。 フラクショナル・ゲートの使用方法、あるいは、使わないようにする方法について詳しくはこちらの資料をご参照ください。

この記事は英語版IBM Researchブログ「New fractional gates reduce circuit depth for utility-scale workloads」(2024年11月日公開)を翻訳し一部更新したものです。

量子中心のスーパーコンピューターに必要なサーキット・カッティングを可能にするダイナミック・サーキット

Natureに掲載された新しい論文は、一つの量子プロセッサーでは実行不可能なサイズの量子回路を、二つの量子プロセッサーを接続して実行できることを世界で初めて示しました。 今日、世界で最も強力な古典的スーパーコンピューター […]

2年前に設定したチャレンジを達成した IBM Quantum

今回が初回となる IBM Quantum Developer Conferenceで、IBMはアルゴリズム探索を容易にする高性能な量子コンピューターと使いやすい量子ソフトウェアを発表しました。 IBM®は 2年前に、量子 […]

量子中心のスーパーコンピューティングの実現

(特別な工夫のない)愚直な古典計算では扱えないレベルの大規模な問題を解決できる能力を持った 実用規模の量子コンピューターが、ハイパフォーマンス・コンピューティングの未来を変えていきます。 歴史上初めて、コン […]