当サイトのクッキーについて IBM のWeb サイトは正常に機能するためにいくつかの Cookie を必要とします(必須)。 このほか、サイト使用状況の分析、ユーザー・エクスペリエンスの向上、広告宣伝のために、お客様の同意を得て、その他の Cookie を使用することがあります。 詳細については、オプションをご確認ください。 IBMのWebサイトにアクセスすることにより、IBMのプライバシー・ステートメントに記載されているように情報を処理することに同意するものとします。 円滑なナビゲーションのため、お客様の Cookie 設定は、 ここに記載されている IBM Web ドメイン間で共有されます。

Data Science and AI

IBM Researchによるディープラーニング推論のための最新アナログAIチップ

2023年08月18日

カテゴリー Data Science and AI | IBM Data and AI | IBM Watson Blog

記事をシェアする:

スケーラブルなアナログ・デジタル混載アーキテクチャーの重要な構成要素となる、エネルギー効率に優れたチップ

図:IBMのアナログAIチップの完成予想図

私たちは、生活や働き方を再定義するAI革命の始まりに立ったばかりです。特に、ディープ・ニューラル・ネットワーク(DNN)はAIの分野に革命をもたらし、基盤モデルや生成AIの登場とともにますます脚光を浴びています。しかし、これらのモデルを従来のデジタル・コンピューティング・アーキテクチャーで実行すると、達成可能な性能やエネルギー効率が制限されてしまいます。AI推論に特化したハードウェアの開発は進んでいますが、これらのアーキテクチャーの多くは、メモリと処理装置を物理的に分割しています。このことは、AIモデルが通常、処理装置から離れたメモリに格納されていて、計算の際にメモリと処理装置間でデータを常にやりとりする必要があるということを意味しています。この手順が計算を遅くし、達成可能な最大エネルギー効率を制限しているのです。

IBM Researchは、AIの計算方法を革新する方法を研究してきました。アナログ・インメモリ・コンピューティングは、あるいは単にアナログAIとも呼ばれますが、生物学的な脳におけるニューラルネットワークの実行方法の主要な特徴を真似ることで、この課題に対処する有望なアプローチです。我々の脳や他の多くの動物の脳では、シナプスの強さ(ニューラルネットワークの場合は「重み」)がニューロン間のコミュニケーションを決定します。アナログAIシステムでは、このシナプスの重みを、相変化メモリ(PCM)のようなナノスケールの抵抗変化型メモリデバイスのコンダクタンスに局所的に保存し、電気回路の法則を利用して積和演算(MAC: Multiply-Accumulate)を行うことで、メモリと処理装置の間で常にデータをやりとりする必要性を軽減します。積和演算はDNNにおける主要な計算演算です。

相変化メモリ(PCM)は、電気パルスを材料に印加するとコンダクタンスが変化することを利用して動作します。材料はアモルファス相と結晶相の間で相変化し、低い電気パルスはデバイスを結晶的に変化させ抵抗値を小さくし、高い電気パルスはデバイスをアモルファスにして抵抗値を大きくします。通常のデジタルなシステムで記録される情報は0または1だけですが、PCMデバイスはアモルファス状態と結晶状態の間の連続した値としてその状態を記録します。この値はシナプス重みと呼ばれ、各PCMの物理的な原子の配置に保存されます。このメモリは不揮発性であるため、電源を切っても重みの値は保持されます。

アナログAIのコンセプトを現実のものにするためには、2つの重要な課題を克服する必要があります。まず、これらのメモリ・アレイは、既存のデジタルなシステムと同等の精度で計算できる必要があります。そして、他のデジタル計算ユニットや、アナログAIチップ上のデジタル通信ファブリックとシームレスにインターフェイスできる必要があります。

8月10日にNature Electronics誌に掲載された論文で、IBM Researchは、さまざまなDNN推論タスクを実行するための最先端のアナログ・デジタル混載AIチップを発表し、こうした課題への対処に向けて重要な一歩を踏み出しました。このチップは、画像処理のAIタスクにおいてデジタル・チップと同等の能力を発揮することが検証された初のアナログ・チップであり、エネルギー効率も大幅に向上しています。

このチップはIBMのアルバニー・ナノテク・コンプレックスで製造され、64個のアナログ・インメモリ・コンピュート・コア(またはタイル)で構成され、各コアには256×256のシナプス・ユニット・セルのクロスバー・アレイが含まれています。各タイルには、アナログとデジタルの世界を移行するためのコンパクトな時間領域アナログ・デジタル・コンバーターが統合されています。各タイルには、単純な非線形ニューロン活性化関数とスケーリング演算を実行する軽量デジタル処理ユニットも統合されています。

各タイルはDNNモデルの1レイヤーに対応する計算を実行できます。シナプスの重みは、PCMデバイスのアナログ・コンダクタンス値としてエンコードされます。チップの中央には、ある種のニューラルネットワークの実行に不可欠な、より複雑な演算を実行するグローバル・デジタル・プロセッシング・ユニットが統合されています。チップはまた、すべてのタイルとグローバル・デジタル・プロセッシング・ユニットのチップ相互接続にデジタル通信経路を持っています。

IBMはこのチップを使用して、アナログ・インメモリ・コンピューティングの計算精度に関して、可能な限り包括的な調査を行い、CIFAR-10画像データセットで92.81%の精度を実証しました。これは私たちの知る限り、現在報告されている同様の技術を用いたチップの中で最高レベルの精度です。また、この論文では、アナログ・インメモリ・コンピューティングを複数のデジタル処理ユニットおよびデジタル通信ファブリックとシームレスに組み合わせる方法も示しました。8ビット入出力の行列乗算について測定された面積あたりスループットは 400 GOPS/mm2 で、抵抗変化型メモリを利用した従来のマルチコアでインメモリのコンピューティング・チップと比べて、エネルギー効率は同等でありながら、15倍以上となりました。

1秒あたりギガ演算回数(GOPS: Giga-operations per second)は、計算効率を表す標準的な指標であり、演算回数を、関与した計算面積で正規化した値になっています。この指標が大きいことは本質的に、ある面積で行われる演算回数が多いこと、すなわちチップが効率的な演算エンジンであることを意味しています。

面積効率にもエネルギー効率にも優れたアナログ/デジタル・コンバーター(ADC)、線形性の高い積和演算、そして2021年のIEEE VLSIシンポジウムで発表した34タイル・チップで披露した超並列データ転送を備えた64タイル・チップのデジタル・コンピュート・ブロックの組み合わせによって、私たちは高速で低消費電力のアナログAI推論アクセラレーター・チップについてのアーキテクチャーのビジョンを実現するために必要な構成要素の多くを実証することができました。

私たちは、これまでに得られた知見に基づいて、今年の初めにIEEE Transactions on VLSI systemsで発表したのと同じようなアクセラレーター・アーキテクチャーを設計しました。私たちのビジョンは、多数のアナログ・インメモリ・コンピューティングのタイルと、超並列2Dメッシュで接続された用途ごとのデジタル・コンピュート・コア群を結合することです。私たちが近年開発したハードウェアを意識した高度な学習処理と連動させることで、これらのアクセラレーターは、今後数年間で、多種多様なニューラルネットワーク・モデルを、ソフトウェアと同等の精度を保ちつつ、高いエネルギー効率を持ったアナログAIハードウェアで実現できるようになると期待しています。

この記事は英語版IBM Researchブログ「IBM Research’s latest analog AI chip for deep learning inference」(2023年8月11日公開)を翻訳し一部更新したものです。

More Data Science and AI stories

敷居もコストも低い! ふくろう販売管理システムがBIダッシュボード機能搭載

IBM Data and AI, IBM Partner Ecosystem

目次 販売管理システムを知名度で選んではいないか? 電子取引データの保存完全義務化の本当の意味 ふくろう販売管理システムは「JIIMA認証」取得済み AIによる売上予測機能にも選択肢を 「眠っているデータの活用」が企業の ...続きを読む

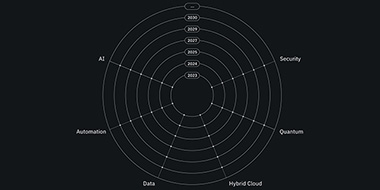

テクノロジーが向かう先とは〜中長期テクノロジー・ロードマップ

IBM Cloud Blog, IBM Data and AI

IBM テクノロジー・ビジョン・ロードマップ – IBM テクノロジー・アトラスを戦略的・技術的な予測にご活用いただけます – IBM テクノロジー・アトラスとは? IBM テクノロジー・アトラス ...続きを読む

データ・ロードマップ

IBM Data and AI

生成AIによるビジネス革新は、オープンなデータストア、フォーマット、エンジン、製品指向のデータファブリック、データ消費を根本的に改善するためのあらゆるレベルでのAIの導入によって促進されます。 2023 オープン・フォー ...続きを読む